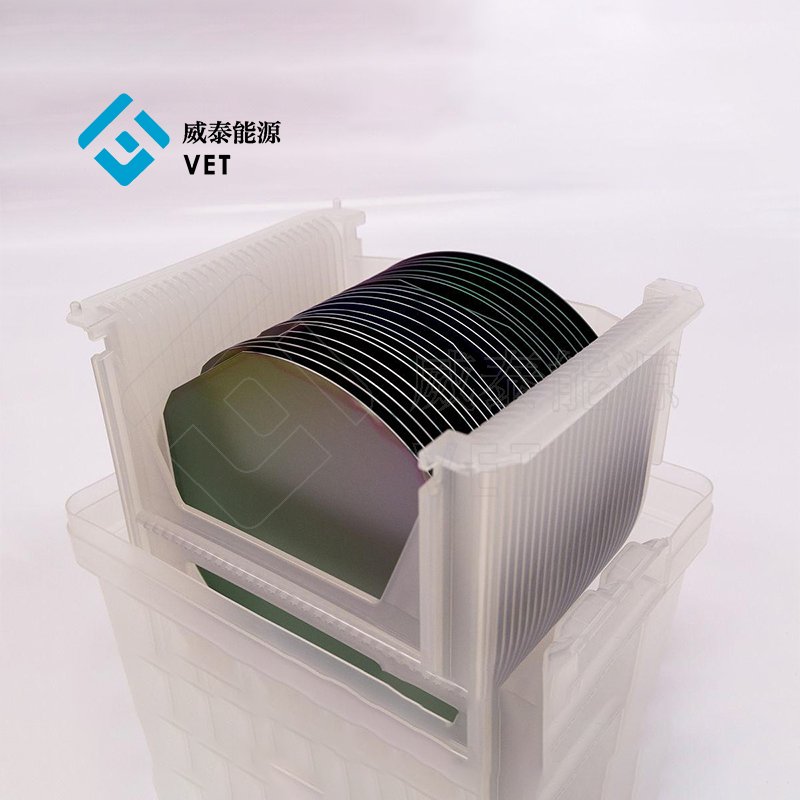

Die 8-Zoll-Silizium-Wafer Typ P ist ein zentraler Bestandteil der modernen Halbleiterfertigung. Mit präzisen Spezifikationen, einschließlich eines 8-Zoll-Durchmessers, Kristallorientierung und Bor-Dotierung, bietet es hervorragende Leistung. Dieser Wafer ist eine vertrauenswürdige Wahl für Anwendungen in CMOS-Technologie, MEMS-Geräten und Leistungselektronik. Seine stabilen elektrischen Eigenschaften und nahtlose Kompatibilität mit fortschrittlichen Materialien, wie 4-Zoll-GaAs-Wafer und 6 Zoll halbisolierende SiC Wafer, machen es wesentlich, zuverlässige und effiziente elektronische komponenten zu schaffen.

| Parameter | Spezifikation |

|---|---|

| Durchmesser | 8 zoll (200 mm) |

| Material | Einfaches Silikon |

| Kristallwachstum Methode | Czochralski (CZ) |

| Kristallorientierung | |

| Art und Weise | P-Typ / Boron |

| Oberfläche | Single-Side Poliert oder Double-Side Poliert |

| Widerstandsfähigkeit | Anpassbar auf Basis der Anwendungsanforderungen |

| Dicke | Standard: 725 μm ± 25 μm |

| Flatness (TTV) | ≤ 5 μm |

| Bogen/Warte | ≤ 30 μm |

| Oberflächenrauhigkeit (Ra) | SSP: < 0,5 nm; DSP: < 0,3 nm |

| Verpackung | Klasse 100 Reinraumverpackung, 25 Wafer pro Kassette |

Die Anpassungsfähigkeit des Wafers erstreckt sich auf Photonik, Optoelektronik und F&D, wo seine hochwertige Oberfläche und thermische Stabilität Präzision und Zuverlässigkeit gewährleisten. Seine Integration mit Materialien wie dem 4 Zoll GaAs Wafer und dem 6 Zoll halbisolierten SiC Wafer verstärkt seine Rolle bei der Förderung der Halbleiterinnovation.

Wichtigste Erkenntnisse

- Der 8 Zoll P-Typ Silikon Wafer ist für halbleiterherstellung, mit einer kristallorientierung und bordotierung für optimale elektrische leistung.

- Anpassbare Widerstandswerte ermöglichen Herstellern, den Wafer für spezifische Anwendungen zu maßgeschneiderten, die Zuverlässigkeit in Geräten wie CMOS-Technologie und MEMS zu verbessern.

- Strenge Sauberkeitsprotokolle und Einhaltung von SEMI-Standards sorgen für hochwertige Wafer, minimieren Defekte und maximierende Ausbeute in fortschrittlichen Halbleiterprozessen.

Kristallgrafik Eigenschaften und Doping

Kristallorientierung und Struktur

Die 8-Zoll-Silizium-Wafer Typ P eine Kristallorientierung, ein Standard in der Halbleiterindustrie. Diese Orientierung bietet isotrope Ätzeigenschaften, die eine Gleichmäßigkeit bei chemischen Ätzprozessen gewährleisten. Seine mechanischen Eigenschaften bieten gleichbleibende Leistung bei hochpräzisen Anwendungen wie Ionenimplantation und Oxidation.

Die einkristalline Siliziumstruktur des Wafers, die nach der Methode Czochralski (CZ) angebaut wird, sorgt für hohe Reinheit und Gleichmäßigkeit. Dieser Prozess erhöht die thermische und mechanische Stabilität des Wafers, so dass er den strengen Bedingungen der Halbleiterfertigung standhält. Die folgende Tabelle zeigt die wichtigsten kristallographischen Eigenschaften:

| Parameter | Spezifikation |

|---|---|

| Durchmesser | 8 zoll (200 mm) |

| Material | Einfaches Silikon |

| Kristallwachstum Methode | Czochralski (CZ) |

| Kristallorientierung | |

| Oberfläche | Single-Side Poliert (SSP) oder Double-Side Poliert (DSP) |

P-Typ Doping-Prozess

Die P-Typ Dotierungsprozess die Einführung von Bor, einem Gruppen-III-Element, in das Siliziumgitter. Dieser Prozess erzeugt „Löcher“, die als die meisten Ladungsträger wirken und die elektrische Leitfähigkeit des Wafers verbessern. Die hohe Konzentration an Bor sorgt auch bei unterschiedlichen Temperaturen für eine stabile elektrische Leistung.

Dieses Dotierungsverfahren ist weit verbreitet in der Herstellung von Dioden, bipolaren Verbindungstransistoren (BJTs) und CMOS-Technologie. Der 8 Inch P Type Silicon Wafer profitiert von diesem Prozess, indem er zuverlässige Leistung in Anwendungen liefert, die präzise elektrische Eigenschaften erfordern.

Widerstandsfähigkeit und seine Rolle in der Performance

Die Widerstandsfähigkeit spielt eine entscheidende Rolle bei der Bestimmung der elektrischen Leistung des 8 Zoll P Type Silicon Wafer. Durch die Anpassung der Widerstandswerte können die Hersteller den Wafer für bestimmte Anwendungen optimieren. Die Bordotierung gewährleistet einen stabilen Widerstand, der für Geräte wie Dioden und CMOS-Schaltungen wesentlich ist.

Die Fähigkeit des Wafers, konsistenten Widerstand über einen weiten Temperaturbereich zu erhalten, erhöht seine Zuverlässigkeit in Hochleistungs-Halbleiteranwendungen. Diese Stabilität gewährleistet die Herstellung effizienter und langlebiger elektronischer Bauteile.

Qualitätsstandards von 8 Zoll P Typ Silikon Wafer

Sauberkeit und Kontaminationskontrolle

Die Aufrechterhaltung der Sauberkeit und die Kontrolle von Verunreinigungen sind entscheidend, um die Zuverlässigkeit des 8 Zoll P Type Silicon Wafer sicherzustellen. Selbst mikroskopische Partikel können die Leistung des Wafers während der Halbleiterherstellung beeinträchtigen. Hersteller halten strenge Protokolle, um Verunreinigungsrisiken zu minimieren.

- Klasse 100 Umwelt: Die Wafer werden in Reinräumen mit maximal 100 Partikeln pro Kubikfuß verarbeitet und verpackt. Dies gewährleistet eine minimale Partikelkontamination.

- Sichere Verpackung: Jeder Wafer wird in eine Kassette gelegt, die typischerweise 25 Wafer hält, und in stickstoffgehärteten Beuteln verschlossen. Dies verhindert Oxidation und Verschmutzung beim Transport.

Diese Maßnahmen stellen sicher, dass die Wafer die hohen Standards erfüllen, die für Anwendungen in der Mikroelektronik und in Solarzellen erforderlich sind.

Planarität und Dicke Gleichmäßigkeit

Planarität und Dickengleichmäßigkeit sind für die Erzielung einer gleichbleibenden Leistung in Halbleiterbauelementen unerlässlich. Der 8 Inch P Type Silicon Wafer erfüllt Industriestandards für die Abflachung und Dickenvariation, wodurch die Kompatibilität mit fortschrittlichen Lithographie- und Ätzprozessen gewährleistet wird.

Maßgeschneiderte Maßstäbe, die von Organisationen wie SEMI und IEC festgelegt werden, geben Toleranzen für Parameter wie Dicke, Flatness und Bogen an. Beispielsweise beträgt die Gesamtdickenvariation (TTV) des Wafers ≤ 5 μm und dessen Bogen/Krieg ≤ 30 μm. Diese präzisen Spezifikationen garantieren die Gleichmäßigkeit über die Waferoberfläche und ermöglichen eine hohe Ausbeute und zuverlässige Geräteleistung.

Gemeinsame Mängel und ihre Auswirkungen auf die Zuverlässigkeit

Defekte in Siliziumwafern können ihre Zuverlässigkeit und Leistung erheblich beeinflussen. In der nachstehenden Tabelle werden häufige Mängel und deren potentielle Auswirkungen beschrieben:

| Typ des Infektions | Beschreibung | Auswirkungen auf Zuverlässigkeit |

|---|---|---|

| Punktfehler | Stellenangebote, Interstitials, Antisite-Defekte, Fremdatome. | Ermöglicht elektrische Eigenschaften und Materialleistung. |

| Verlagerungen | Ursprung während des Schüttkristallwachstums durch thermische Belastung und andere Faktoren. | Kann zu strukturellen Schwächen und Ausfall bei Geräten führen. |

| Stapelfehler | Flaws in der Stapelfolge von Atomebenen im Kristallgitter. | Kompromisst die Integrität der Kristallstruktur. |

| Zwillinge | Bereiche im Kristall, die Spiegelreflexionen sind. | Kann die mechanischen Eigenschaften des Wafers beeinflussen. |

| Einschlüsse | Ausländische Partikel im Silizium. | Kann Mängel im Endprodukt verursachen. |

| Rezepte | Feste Partikel, die sich innerhalb des Siliciums bilden. | Kann zu Zuverlässigkeitsfragen in elektronischen Anwendungen führen. |

| Mikrodefekte | Kleine Defekte, die schwer zu erkennen sind. | Kann die Gesamtleistung und Zuverlässigkeit beeinflussen. |

Hersteller implementieren strenge Qualitätsprüfungen, um diese Mängel zu identifizieren und zu mildern, um sicherzustellen, dass die Wafer den höchsten Standards der Zuverlässigkeit und Leistung entsprechen.

Wafer Grades und Anwendungen

Prime Grade Wafer für hochpräzise Anwendungen

Primäre Wafer die Qualität in der Halbleiterherstellung darstellen. Diese Wafer weisen eine außergewöhnliche Planheit, eine minimale Verschmutzung und eine überlegene Fehlerkontrolle auf, was sie für hochpräzise Anwendungen unverzichtbar macht. Ihre doppelseitige polierte (DSP) Oberfläche sorgt für Gleichmäßigkeit, die für fortgeschrittene Prozesse wie Photolithographie und Ätzen kritisch ist.

Primäre Wafer sind weit verbreitet bei der Herstellung von halbleiterbauelemente, MEMS und optoelektronische Komponenten. So sind ihre stabilen elektrischen Eigenschaften ideal für integrierte Schaltungen, während ihre präzise Oberflächenveredelung die Herstellung von Beschleunigungsmessern und Gyroskopen unterstützt. Die folgende Tabelle verdeutlicht ihre primären Anwendungen:

| Anwendungsart | Beschreibung |

|---|---|

| Halbleiterbauelemente | Formt das Basismaterial für integrierte Schaltungen, einschließlich Prozessoren und Speichereinrichtungen. |

| MENSCHEN | Ideal für Geräte wie Beschleunigungsmesser und Gyroskope durch präzise Oberflächenbearbeitung. |

| Photonik und Optoelektronik | Verwendet in optischen Sensoren, LEDs und Photovoltaikzellen, profitieren von stabilen elektrischen Eigenschaften. |

| FuE und Prototypen | Hochwertige Oberflächen und elektrische Eigenschaften machen es für Forschung und Entwicklung geeignet. |

Test Grade Wafer für Experimentelle Verwendung

Prüfwafer dienen als kostengünstige Lösung für experimentelle und nichtkritische Anwendungen. Diese Wafer, oft einseitig poliert (SSP), werden in der Gerätekalibrierung, Prozesstests und Trainingszwecken verwendet. Während sie nicht den strengen Standards der erstklassigen Wafer entsprechen, bieten sie ausreichend Qualität für Aufgaben, die keine hohe Präzision erfordern.

Hersteller verwenden oft Test-Sorten-Wafer, um Produktionsprozesse zu optimieren, bevor Sie zu erstklassigen Wafern wechseln. Dieser Ansatz minimiert den Abfall und reduziert die Kosten während der ersten Stufen der Halbleiterfertigung.

Reclaimed Wafers und ihre kosteneffizienten Anwendungen

Reclaimed Wafer bieten eine umweltfreundliche und kostengünstige Alternative für verschiedene Anwendungen. Diese Wafer durchlaufen einen strengen Reinigungs- und Polierprozess, um ihre Oberflächenqualität wiederherzustellen, wodurch sie für unkritische Aufgaben geeignet sind.

- Reclaimed Wafer reduzieren die Kosten auf ein Drittel oder ein Viertel der neuen Prime-Testwafer.

- Sie werden häufig für die Partikelüberwachung, Diffusionsprozesse und Geräteaufbau verwendet.

- Die großen Hersteller berichten über erhebliche Einsparungen, indem sie wiedergewonnene Wafer in ihren Betrieb aufnehmen.

Obwohl wiedergewonnene Wafer nicht mit der Qualität der erstklassigen Wafer übereinstimmen, bieten sie eine praktische Lösung für Anwendungen, bei denen eine hohe Präzision nicht wesentlich ist. Ihr Einsatz unterstützt nachhaltige Praktiken in der Halbleiterindustrie, indem Materialabfälle reduziert werden.

Backside Behandlungen für verbesserte Leistung

Rückenätzung für Stressentlastung

Bei der Leistungssteigerung von Siliziumwafern spielt das Backside Ätzen eine entscheidende Rolle. Bei diesem Verfahren wird das Material von der hinteren Oberfläche des Wafers entfernt, was zur Linderung der inneren Spannung beiträgt. Durch die Verringerung der Belastung verhindert das Hinterätzen das Verneben und sorgt für eine bessere Abflachung. Die Erzielung präziser Abmessungen und Oberflächengüte ist für die Halbleiterfertigung von wesentlicher Bedeutung, da sie die Zuverlässigkeit der Geräte unmittelbar beeinflusst. Hersteller verlassen sich auf diese Technik, um die strukturelle Integrität des 8 Zoll P Type Silicon Wafer bei Hochtemperaturprozessen zu erhalten.

Gettering-Techniken zur Verbesserung des Ertrags

Gettering-Techniken sind für die Verbesserung der Ausbeute von Silizium-Wafern durch die Verwaltung von Metall-Verunreinigungen unerlässlich. Diese Methoden schaffen bevorzugte Stellen für die Metallausscheidung von empfindlichen Bereichen des Wafers. Durch die Ausrichtung von Verunreinigungen auf weniger kritische Regionen erhöht Gettering die Gesamtqualität und Leistung des Wafers. Für P-Silicium-Wafer sorgt dieser Ansatz dafür, dass die Frontfläche fehlerfrei bleibt, was für die Herstellung von Hochleistungs-Halbleitergeräten von entscheidender Bedeutung ist. Hersteller implementieren diese Techniken, um die Ausbeute zu maximieren und die Zuverlässigkeit ihrer Produkte zu erhalten.

Polier- und Oberflächenbearbeitung für defektfreie Wafer

Polieren und Oberflächenveredelung sind kritische Schritte, um fehlerfreie Wafer zu gewährleisten. Die chemische mechanische Planarisierung (CMP) reduziert die Oberflächenrauhigkeit und erreicht eine spiegelartige Oberfläche, die für nachfolgende Fertigungsschritte wesentlich ist. Dieser Prozess minimiert auch die Gesamtdickenvariation (TTV), wodurch die Gleichmäßigkeit über den Wafer gewährleistet wird. Das Polieren entfernt Fehler, die durch Schleifen verursacht werden, trägt zur Reduzierung der Scheibendicke bei und sorgt für eine flache, fehlerfreie Oberfläche. Diese Eigenschaften sind für den 8 Zoll P Type Silicon Wafer unerlässlich, da sie zuverlässige Verbindungen in Halbleiterbauelementen ermöglichen und fortschrittliche Fertigungsprozesse unterstützen.

SEMI Standards für 8 Zoll P Typ Silikon Wafer

Abmessungen und Toleranzen

SEMI-Standards definieren präzise Maßtoleranzen für den 8 Zoll P Type Silicon Wafer, um die Kompatibilität mit fortschrittlichen Halbleiterherstellungsprozessen zu gewährleisten. Diese Standards garantieren Gleichmäßigkeit in Waferabmessungen, die für die Erzielung hoher Ausbeuten bei der Gerätefertigung von entscheidender Bedeutung sind. Die folgende Tabelle beschreibt die wichtigsten Maßangaben:

| Spezifikation | Wert |

|---|---|

| Durchmesser | 200 mm ± 0,2 mm |

| WIE | ≤ 30 μm |

| WAHL | ≤ 30 μm |

| Gesamtdickenvariation (TTV) | ≤ 5μm |

| Partikel | ≤ 50@≥0.16μm |

Diese Toleranzen sorgen dafür, dass Wafer die strengen Anforderungen moderner Lithographie- und Ätzprozesse erfüllen. Hersteller verlassen sich auf diese Standards, um Wafer mit gleichbleibender Qualität und Leistung zu produzieren.

Einhaltung der elektrischen und mechanischen Eigenschaften

SEMI-Standards setzen sich auch mit den elektrischen und mechanischen Eigenschaften von Silizium-Wafern auseinander und gewährleisten ihre Eignung für verschiedene Anwendungen. Die wichtigsten Compliance-Maßnahmen umfassen:

- Toleranzen für Durchmesser, Dicke und Abflachung zur Aufrechterhaltung der Maßgenauigkeit.

- Bestimmen Sie akzeptable Mengen an Verunreinigungen und kristalline Fehler, um die Zuverlässigkeit und Langlebigkeit zu verbessern.

- Überprüfung elektrischer Eigenschaften wie Widerstandsfähigkeit und Trägerkonzentration durch strenge Qualitätsprüfung.

Diese Maßnahmen sorgen dafür, dass der 8-Zoll-P-Typ-Silicon Wafer stabile Leistung in Anwendungen wie Mikroelektronik und Solarzellen liefert. Die Einhaltung dieser Standards minimiert Fehler und erhöht die Gesamteffizienz von Halbleiterbauelementen.

Bedeutung der Einhaltung der SEMI-Leitlinien

Die Einhaltung von SEMI-Richtlinien ist für Hersteller unerlässlich, die hochwertige Siliziumwafer produzieren wollen. Diese Standards bieten einen umfassenden Rahmen, der die Fertigung, Verpackung und Handhabung umfasst. Durch die folgenden SEMI-Richtlinien gewährleisten Hersteller die Stabilität und Leistungsfähigkeit von Wafern in unterschiedlichen Anwendungen.

Die Halbleiterindustrie verlangt Einheitlichkeit und Interoperabilität durch schnelle Innovation und die Notwendigkeit einer gesteigerten Leistung. SEMI-Standards helfen Herstellern, diese Anforderungen zu erfüllen, indem sie Effizienz und Konsistenz in der Produktion fördern. Für den 8 Zoll P Type Silicon Wafer sorgt die Einhaltung dieser Richtlinien für seine Zuverlässigkeit bei fortschrittlichen Technologien wie CMOS-Geräten und MEMS.

Der 8 Zoll P Type Silicon Wafer zeichnet Präzision und Zuverlässigkeit in der Halbleiterfertigung aus. Seine kritischen Spezifikationen, wie Kristallorientierung, Bor-Dotierung und anpassbare Widerstandskraft, sorgen für optimale Leistung bei Anwendungen wie CMOS-Technologie, MEMS und Power-Geräten.

ET Energie liefert Wafer, die strenge Industriestandards durch fortschrittliche Materialien und sorgfältige Engineering erfüllen. Ihr Qualitätsengagement minimiert Fehler und erhöht die Wafersicherheit und unterstützt eine hohe Ausbeute.

Diese Wafer spielen eine zentrale Rolle bei der Entwicklung von Halbleiterbauelementen, erneuerbaren Energiesystemen und der Automobilelektronik. Ihre stabilen elektrischen Eigenschaften und Kompatibilität mit modernsten Technologien treiben Innovation und Effizienz in modernen elektronischen Anwendungen.

FAQ

Was macht den 8 Zoll P Type Silicon Wafer für die Halbleiterfertigung geeignet?

Seine Kristallorientierung, Bordotierung und anpassbare Widerstandskraft sorgen für hohe Präzision, thermische Stabilität und zuverlässige elektrische Leistung für fortgeschrittene Halbleiteranwendungen.

Kann der Wafer für spezielle Anwendungen angepasst werden?

Ja, VET Energieangebot anpassungsoptionen für Widerstand, Dicke und Dotierung, um unterschiedliche Fertigungsanforderungen zu erfüllen, einschließlich CMOS-Geräte, MEMS und Solarzellen.

Wie gewährleistet VET Energy die Waferqualität?

ET Energie achtet auf SEMI-Standards, setzt fortschrittliche Poliertechniken ein und führt strenge Qualitätsprüfungen durch, um Fehler zu minimieren und eine gleichbleibende Leistung über alle Wafer zu gewährleisten.