The 8 Inch P Type Silicon Wafer from VET Energy is a high-performance silicon wafer designed for a wide range of semiconductor applications, including solar cells, MEMS devices, and integrated circuits. Known for its excellent electrical conductivity and consistent performance, this wafer is the preferred choice for manufacturers looking to produce reliable and efficient electronic components. VET Energy ensures precise doping levels and a high-quality surface finish for optimal device fabrication.

These 8 Inch P Type Silicon Wafers are fully compatible with various materials like SiC Substrate, SOI Wafer, SiN Substrate, and are suitable for Epi Wafer growth, ensuring versatility for advanced semiconductor manufacturing processes. The wafers can also be used in conjunction with other high-tech materials like Gallium Oxide Ga2O3 and AlN Wafer, making them ideal for next-generation electronic applications. Their robust design also fits seamlessly into Cassette-based systems, ensuring efficient and high-volume production handling.

VET Energy provides customers with customized wafer solutions. We can customize wafers with different resistivity, oxygen content, thickness, etc. according to customers’ specific needs. In addition, we also provide professional technical support and after-sales service to help customers solve various problems encountered during the production process.

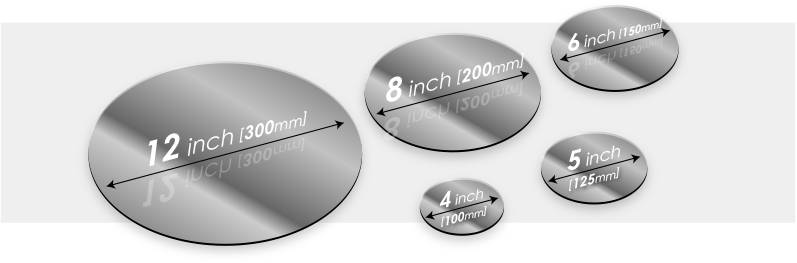

WAFERING SPECIFICATIONS

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Grade,Sl=Semi-lnsulating

|

Item |

8-Inch |

6-Inch |

4-Inch |

||

|

n-P |

n-Pm |

n-Ps |

SI |

SI |

|

|

TTV(GBIR) |

≤6um |

≤6um |

|||

|

Bow(GF3YFCD)-Absolute Value |

≤15μm |

≤15μm |

≤25μm |

≤15μm |

|

|

Warp(GF3YFER) |

≤25μm |

≤25μm |

≤40μm |

≤25μm |

|

|

LTV(SBIR)-10mmx10mm |

<2μm |

||||

|

Wafer Edge |

Beveling |

||||

SURFACE FINISH

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Grade,Sl=Semi-lnsulating

|

Item |

8-Inch |

6-Inch |

4-Inch |

||

|

n-P |

n-Pm |

n-Ps |

SI |

SI |

|

|

Surface Finish |

Double side Optical Polish,Si- Face CMP |

||||

|

SurfaceRoughness |

(10um x 10um) Si-FaceRa≤0.2nm |

(5umx5um) Si-Face Ra≤0.2nm |

|||

|

Edge Chips |

None Permitted (length and width≥0.5mm) |

||||

|

Indents |

None Permitted |

||||

|

Scratches(Si-Face) |

Qty.≤5,Cumulative |

Qty.≤5,Cumulative |

Qty.≤5,Cumulative |

||

|

Cracks |

None Permitted |

||||

|

Edge Exclusion |

3mm |

||||