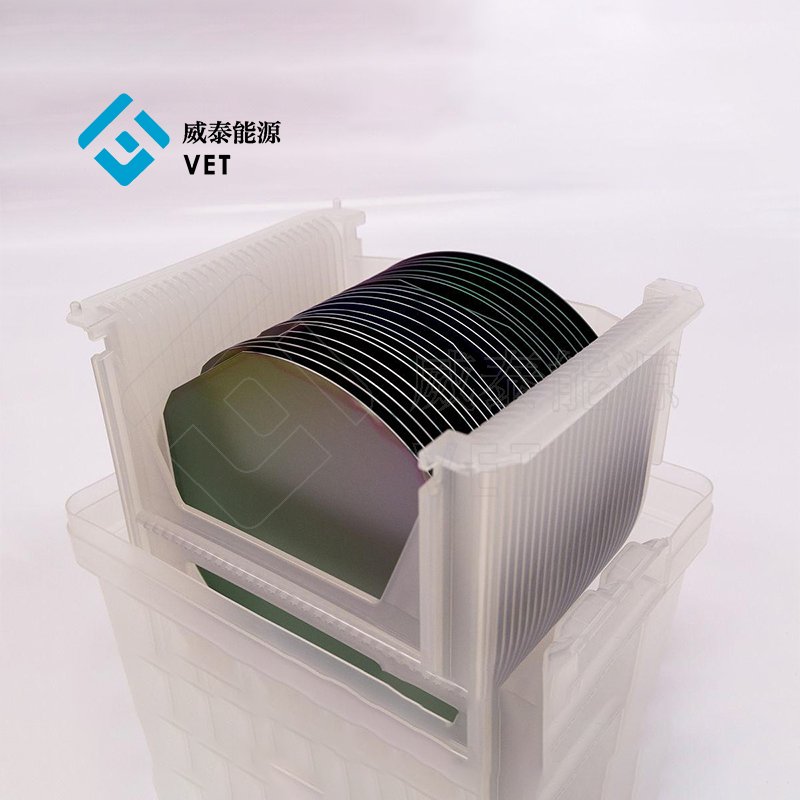

The 8 Inch P Type Silicon Wafer is a pivotal component in contemporary semiconductor manufacturing. With precise specifications, including an 8-inch diameter, <100> crystal orientation, and boron doping, it delivers outstanding performance. This wafer is a trusted choice for applications in CMOS technology, MEMS devices, and power electronics. Its stable electrical properties and seamless compatibility with advanced materials, such as the 4 Inch GaAs Wafer and the 6 Inch semi insulating SiC Wafer, make it essential for creating reliable and efficient electronic components.

| Parameter | Specification |

|---|---|

| Diameter | 8-inch (200 mm) |

| Material | Single-Crystal Silicon |

| Crystal Growth Method | Czochralski (CZ) |

| Crystal Orientation | <100> |

| Type/Dopant | P-Type / Boron |

| Surface Finish | Single-Side Polished or Double-Side Polished |

| Resistivity | Customizable based on application needs |

| Thickness | Standard: 725 µm ± 25 µm |

| Flatness (TTV) | ≤ 5 µm |

| Bow/Warp | ≤ 30 µm |

| Surface Roughness (Ra) | SSP: < 0.5 nm; DSP: < 0.3 nm |

| Packaging | Class 100 cleanroom packaging, 25 wafers per cassette |

The wafer’s adaptability extends to photonics, optoelectronics, and R&D, where its high-quality surface and thermal stability ensure precision and reliability. Its integration with materials like the 4 Inch GaAs Wafer and the 6 Inch semi insulating SiC Wafer further enhances its role in advancing semiconductor innovation.

Key Takeaways

- The 8 Inch P Type Silicon Wafer is essential for semiconductor manufacturing, featuring a <100> crystal orientation and boron doping for optimal electrical performance.

- Customizable resistivity levels allow manufacturers to tailor the wafer for specific applications, enhancing reliability in devices like CMOS technology and MEMS.

- Strict cleanliness protocols and adherence to SEMI standards ensure high-quality wafers, minimizing defects and maximizing yield in advanced semiconductor processes.

Crystallographic Properties and Doping

Crystal Orientation and Structure

The 8 Inch P Type Silicon Wafer features a <100> crystal orientation, a standard in the semiconductor industry. This orientation offers isotropic etching properties, which ensure uniformity during chemical etching processes. Its mechanical characteristics provide consistent performance in high-precision applications like ion implantation and oxidation.

The wafer’s single-crystal silicon structure, grown using the Czochralski (CZ) method, ensures high purity and uniformity. This process enhances the wafer’s thermal and mechanical stability, enabling it to withstand the rigorous conditions of semiconductor fabrication. The table below highlights the key crystallographic properties:

| Parameter | Specification |

|---|---|

| Diameter | 8-inch (200 mm) |

| Material | Single-Crystal Silicon |

| Crystal Growth Method | Czochralski (CZ) |

| Crystal Orientation | <100> |

| Surface Finish | Single-Side Polished (SSP) or Double-Side Polished (DSP) |

P-Type Doping Process

The P-Type doping process involves introducing boron, a Group III element, into the silicon lattice. This process creates “holes,” which act as the majority charge carriers, enhancing the wafer’s electrical conductivity. The high concentration of boron ensures stable electrical performance, even under varying temperatures.

This doping method is widely used in manufacturing diodes, bipolar junction transistors (BJTs), and CMOS technology. The 8 Inch P Type Silicon Wafer benefits from this process by delivering reliable performance in applications requiring precise electrical properties.

Resistivity and Its Role in Performance

Resistivity plays a critical role in determining the electrical performance of the 8 Inch P Type Silicon Wafer. By customizing resistivity levels, manufacturers can optimize the wafer for specific applications. The boron doping ensures stable resistivity, which is essential for devices like diodes and CMOS circuits.

The wafer’s ability to maintain consistent resistivity across a wide temperature range enhances its reliability in high-performance semiconductor applications. This stability ensures the production of efficient and durable electronic components.

Quality Standards of 8 Inch P Type Silicon Wafer

Cleanliness and Contamination Control

Maintaining cleanliness and controlling contamination are critical for ensuring the reliability of the 8 Inch P Type Silicon Wafer. Even microscopic particles can compromise the wafer’s performance during semiconductor fabrication. Manufacturers adhere to stringent protocols to minimize contamination risks.

- Class 100 Environment: Wafers are processed and packaged in cleanrooms with a maximum of 100 particles per cubic foot of air. This ensures minimal particle contamination.

- Secure Packaging: Each wafer is placed in a cassette, typically holding 25 wafers, and sealed in nitrogen-purged bags. This prevents oxidation and contamination during transportation.

These measures ensure that the wafers meet the high standards required for applications in microelectronics and solar cells.

Planarity and Thickness Uniformity

Planarity and thickness uniformity are essential for achieving consistent performance in semiconductor devices. The 8 Inch P Type Silicon Wafer meets industry standards for flatness and thickness variation, ensuring compatibility with advanced lithography and etching processes.

Dimensional standards, established by organizations like SEMI and IEC, specify tolerances for parameters such as thickness, flatness, and bow. For example, the wafer’s total thickness variation (TTV) is ≤5 µm, and its bow/warp is ≤30 µm. These precise specifications guarantee uniformity across the wafer surface, enabling high-yield production and reliable device performance.

Common Defects and Their Impact on Reliability

Defects in silicon wafers can significantly affect their reliability and performance. The table below outlines common defects and their potential impacts:

| Defect Type | Description | Impact on Reliability |

|---|---|---|

| Point Defects | Vacancies, interstitials, antisite defects, foreign atoms. | Affects electrical properties and material performance. |

| Dislocations | Originate during bulk crystal growth due to thermal stress and other factors. | Can lead to structural weaknesses and failure in devices. |

| Stacking Faults | Flaws in the stacking sequence of atomic planes in the crystal lattice. | Compromises the integrity of the crystal structure. |

| Twins | Regions in the crystal that are mirror reflections of each other. | Can affect the mechanical properties of the wafer. |

| Inclusions | Foreign particles within the silicon. | May cause defects in the final product. |

| Precipitates | Solid particles that form within the silicon. | Can lead to reliability issues in electronic applications. |

| Microdefects | Small-scale defects that can be difficult to detect. | May impact the overall performance and reliability. |

Manufacturers implement rigorous quality testing to identify and mitigate these defects, ensuring that the wafers meet the highest standards of reliability and performance.

Wafer Grades and Applications

Prime Grade Wafers for High-Precision Applications

Prime grade wafers represent the pinnacle of quality in semiconductor manufacturing. These wafers exhibit exceptional flatness, minimal contamination, and superior defect control, making them indispensable for high-precision applications. Their double-sided polished (DSP) surface ensures uniformity, which is critical for advanced processes like photolithography and etching.

Prime grade wafers are widely used in the production of semiconductor devices, MEMS, and optoelectronic components. For instance, their stable electrical properties make them ideal for integrated circuits, while their precise surface finish supports the fabrication of accelerometers and gyroscopes. The table below highlights their primary applications:

| Application Type | Description |

|---|---|

| Semiconductor Devices | Forms the base material for integrated circuits, including processors and memory devices. |

| MEMS | Ideal for devices like accelerometers and gyroscopes due to precise surface finishing. |

| Photonics and Optoelectronics | Used in optical sensors, LEDs, and photovoltaic cells, benefiting from stable electrical properties. |

| R&D and Prototyping | High-quality surface and electrical characteristics make it suitable for research and development. |

Test Grade Wafers for Experimental Use

Test grade wafers serve as a cost-effective solution for experimental and non-critical applications. These wafers, often single-side polished (SSP), are used in equipment calibration, process testing, and training purposes. While they do not meet the stringent standards of prime grade wafers, they provide sufficient quality for tasks that do not require high precision.

Manufacturers often utilize test grade wafers to optimize production processes before transitioning to prime grade wafers. This approach minimizes waste and reduces costs during the initial stages of semiconductor fabrication.

Reclaimed Wafers and Their Cost-Effective Applications

Reclaimed wafers offer an environmentally friendly and economical alternative for various applications. These wafers undergo a rigorous cleaning and polishing process to restore their surface quality, making them suitable for non-critical tasks.

- Reclaimed wafers reduce costs to one-third or one-fourth of new prime test wafers.

- They are commonly used for particle monitoring, diffusion processes, and equipment setup.

- Major manufacturers report significant savings by incorporating reclaimed wafers into their operations.

Although reclaimed wafers may not match the quality of prime grade wafers, they provide a practical solution for applications where high precision is not essential. Their use supports sustainable practices in the semiconductor industry by reducing material waste.

Backside Treatments for Enhanced Performance

Backside Etching for Stress Relief

Backside etching plays a crucial role in enhancing the performance of silicon wafers. This process involves removing material from the back surface of the wafer, which helps alleviate internal stress. By reducing stress, backside etching prevents bowing and ensures better flatness. Achieving precise dimensions and surface quality is essential in semiconductor manufacturing, as it directly impacts the reliability of devices. Manufacturers rely on this technique to maintain the structural integrity of the 8 Inch P Type Silicon Wafer during high-temperature processes.

Gettering Techniques to Improve Yield

Gettering techniques are essential for improving the yield of silicon wafers by managing metal impurities. These methods create preferential sites for metal precipitation away from sensitive areas of the wafer. By directing impurities to less critical regions, gettering enhances the overall quality and performance of the wafer. For P-type silicon wafers, this approach ensures that the front surface remains free of defects, which is vital for producing high-performance semiconductor devices. Manufacturers implement these techniques to maximize yield and maintain the reliability of their products.

Polishing and Surface Finishing for Defect-Free Wafers

Polishing and surface finishing are critical steps in ensuring defect-free wafers. Chemical mechanical planarization (CMP) reduces surface roughness and achieves a mirror-like finish, which is essential for subsequent manufacturing steps. This process also minimizes total thickness variation (TTV), ensuring uniformity across the wafer. Polishing removes defects caused by grinding, contributes to reducing wafer thickness, and provides a flat, defect-free surface. These qualities are indispensable for the 8 Inch P Type Silicon Wafer, as they enable reliable connections in semiconductor devices and support advanced fabrication processes.

SEMI Standards for 8 Inch P Type Silicon Wafer

Dimensional Standards and Tolerances

SEMI standards define precise dimensional tolerances for the 8 Inch P Type Silicon Wafer to ensure compatibility with advanced semiconductor manufacturing processes. These standards guarantee uniformity in wafer dimensions, which is critical for achieving high yields in device fabrication. The table below outlines the key dimensional specifications:

| Specification | Value |

|---|---|

| Diameter | 200mm ± 0.2mm |

| BOW | ≤ 30µm |

| WARP | ≤ 30µm |

| Total Thickness Variation (TTV) | ≤ 5µm |

| Particles | ≤ 50@≥0.16µm |

These tolerances ensure that wafers meet the stringent requirements of modern lithography and etching processes. Manufacturers rely on these standards to produce wafers with consistent quality and performance.

Electrical and Mechanical Properties Compliance

SEMI standards also address the electrical and mechanical properties of silicon wafers, ensuring their suitability for various applications. Key compliance measures include:

- Specifying tolerances for diameter, thickness, and flatness to maintain dimensional accuracy.

- Defining acceptable levels of impurities and crystalline flaws to enhance reliability and longevity.

- Verifying electrical properties such as resistivity and carrier concentration through rigorous quality testing.

These measures ensure that the 8 Inch P Type Silicon Wafer delivers stable performance in applications like microelectronics and solar cells. Adherence to these standards minimizes defects and enhances the overall efficiency of semiconductor devices.

Importance of Adhering to SEMI Guidelines

Adhering to SEMI guidelines is essential for manufacturers aiming to produce high-quality silicon wafers. These standards provide a comprehensive framework that covers fabrication, packaging, and handling. By following SEMI guidelines, manufacturers ensure the stability and performance of wafers across diverse applications.

The semiconductor industry demands uniformity and interoperability due to rapid innovation and the need for enhanced performance. SEMI standards help manufacturers meet these demands by promoting efficiency and consistency in production. For the 8 Inch P Type Silicon Wafer, compliance with these guidelines ensures its reliability in advancing technologies like CMOS devices and MEMS.

The 8 Inch P Type Silicon Wafer exemplifies precision and reliability in semiconductor manufacturing. Its critical specifications, such as <100> crystal orientation, boron doping, and customizable resistivity, ensure optimal performance across applications like CMOS technology, MEMS, and power devices.

VET Energy delivers wafers that meet stringent industry standards through advanced materials and meticulous engineering. Their commitment to quality minimizes defects and enhances wafer reliability, supporting high-yield production.

These wafers play a pivotal role in advancing semiconductor devices, renewable energy systems, and automotive electronics. Their stable electrical properties and compatibility with cutting-edge technologies drive innovation and efficiency in modern electronic applications.

FAQ

What makes the 8 Inch P Type Silicon Wafer suitable for semiconductor manufacturing?

Its <100> crystal orientation, boron doping, and customizable resistivity ensure high precision, thermal stability, and reliable electrical performance for advanced semiconductor applications.

Can the wafer be customized for specific applications?

Yes, VET Energy offers customization options for resistivity, thickness, and doping levels to meet diverse manufacturing requirements, including CMOS devices, MEMS, and solar cells.

How does VET Energy ensure wafer quality?

VET Energy adheres to SEMI standards, employs advanced polishing techniques, and conducts rigorous quality testing to minimize defects and ensure consistent performance across all wafers.